Xentium DSP Radiation-hardened IP core

During scientific missions into deep space, modern instruments and sensors gather so much data that it cannot be communicated back to earth in its entirety. This is why the data has to be analyzed and compressed on-board in space before being relayed back to earth. The digital components that perform these tasks have to be able to withstand the corrupting consequences of cosmic radiation. Only radiation-hardened equipment is suitable for space missions. Our Xentium Digital Signal Processor IP core was designed with the harsh circumstances of deep space in mind. This extremely reliable, fault-tolerant processor IP core will do its job even in the toughest circumstances.

Our radiation-hardened IP cores

Rad-hard data processor IP

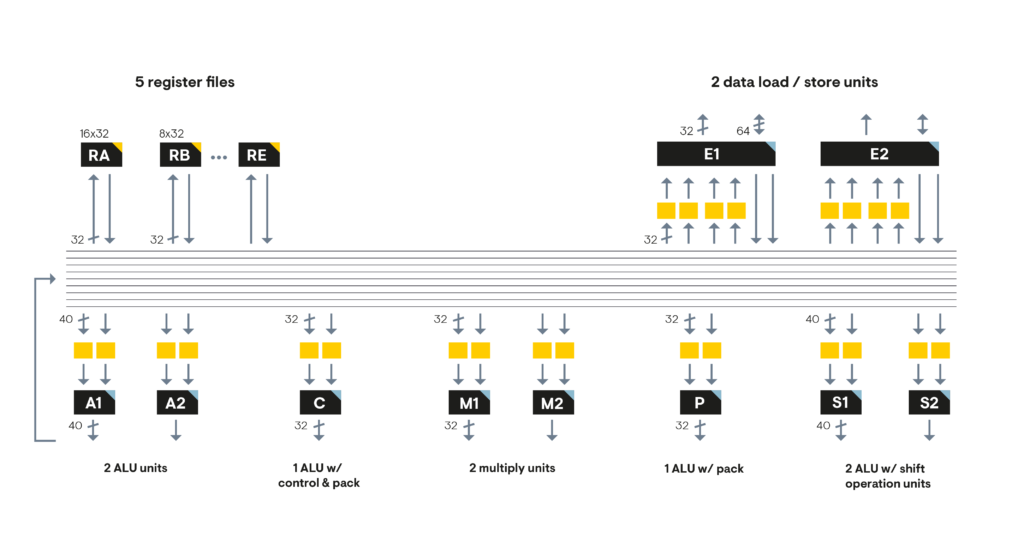

The Xentium is a high-performance, low-energy-consumption VLIW (Very Long Instruction Word) DSP core. The main advantage of this VLIW core is that it moves complexity from the hardware to the compiler, which means the hardware can be smaller and more energy-efficient. The Xentium supports 32-bit fixed-point operations, as well as single-precision fused multiply-add (FMA) operations. It is a highly scalable IP building block, suited for large multi-core systems-on-chip (SoC). The Xentium can also be used as DSP accelerator in combination with a general purpose processor, such as the FreNox RISC-V.

The Xentium combines high computational power with low energy consumption and a small silicon footprint. Advanced loop control mechanisms reduce code size and increase energy efficiency by switching off idle components during loop execution. The use of tightly coupled data memory contributes to even lower energy consumption and higher processing efficiency. The Xentium DSP IP core comes with a C-based Software Development Environment (SDE), including a toolchain consisting of a C compiler with standard C library, an assembler, a linker, a simulator, a debugger and a number of other utilities.

Developed with the European Space Agency ESA

The Xentium DSP IP Core was developed in close cooperation with the European Space Agency ESA. ESA needed a standard ASIC with a space-qualified, radiation-hardened Digital Signal Processor and a performance of at least 1 GFLOPS (one billion floating-point operations per second) for its Cosmic Vision program. Before implementing the multi-core DSP SoC architecture in rad hard silicium technology, it’s functionality was validated using a prototype based on commercial FPGA technology. The multi-stage development project resulted in a reliable, fault-tolerant, radiation-resistant data processor IP for on-board sensor data processing with state-of-the-art processing power.

FPGA with multi-core Xentium SoC architecture

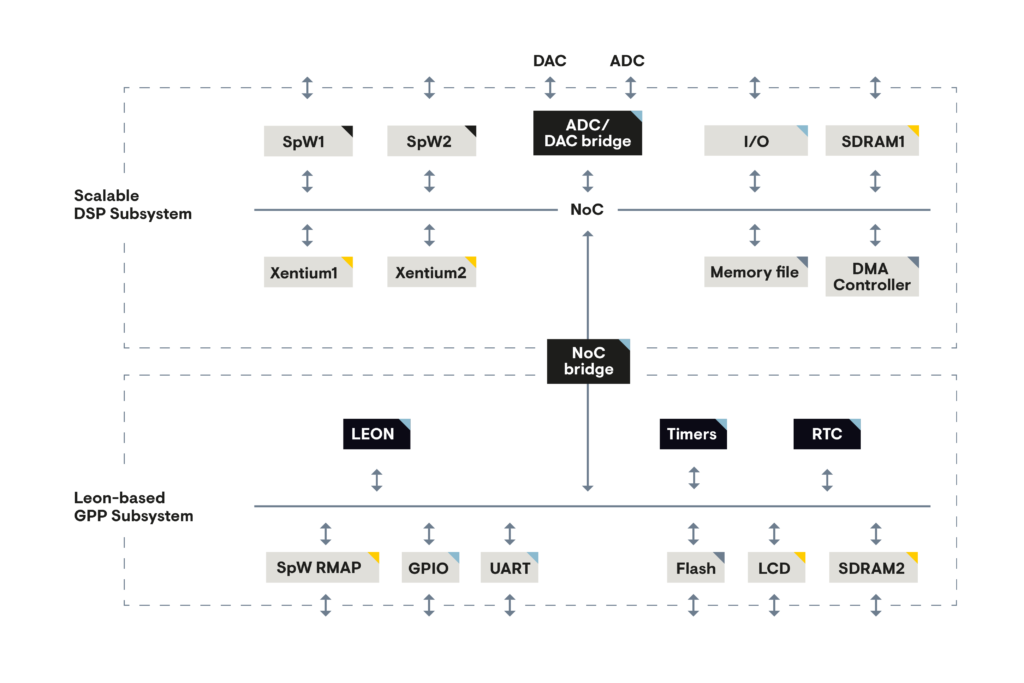

We developed a functional payload unit prototype of a reliable data processor for space missions based on our Xentium DSP IP. The prototype was implemented using commercial FPGA technology to validate the functional aspects of the multi-core DSP SoC architecture.

The prototype was able to withstand data errors on the software level as well as on the hardware level. The architecture comprised a System-on-Chip integrating multiple Xentium DSP cores, SpaceWire interfaces (including RMAP protocol support), CCSDS timers, ADC/DAC interfaces, LEON processor, and EDAC-protected on-chip as well as off-chip memories, all in one system.

In general, data interfaces are connected directly to the Network-on-Chip of the Xentium DSP subsystem, and control interfaces and peripherals are placed on the bus of the general purpose processor (GPP) subsystem.

Radiation-hardened ASIC

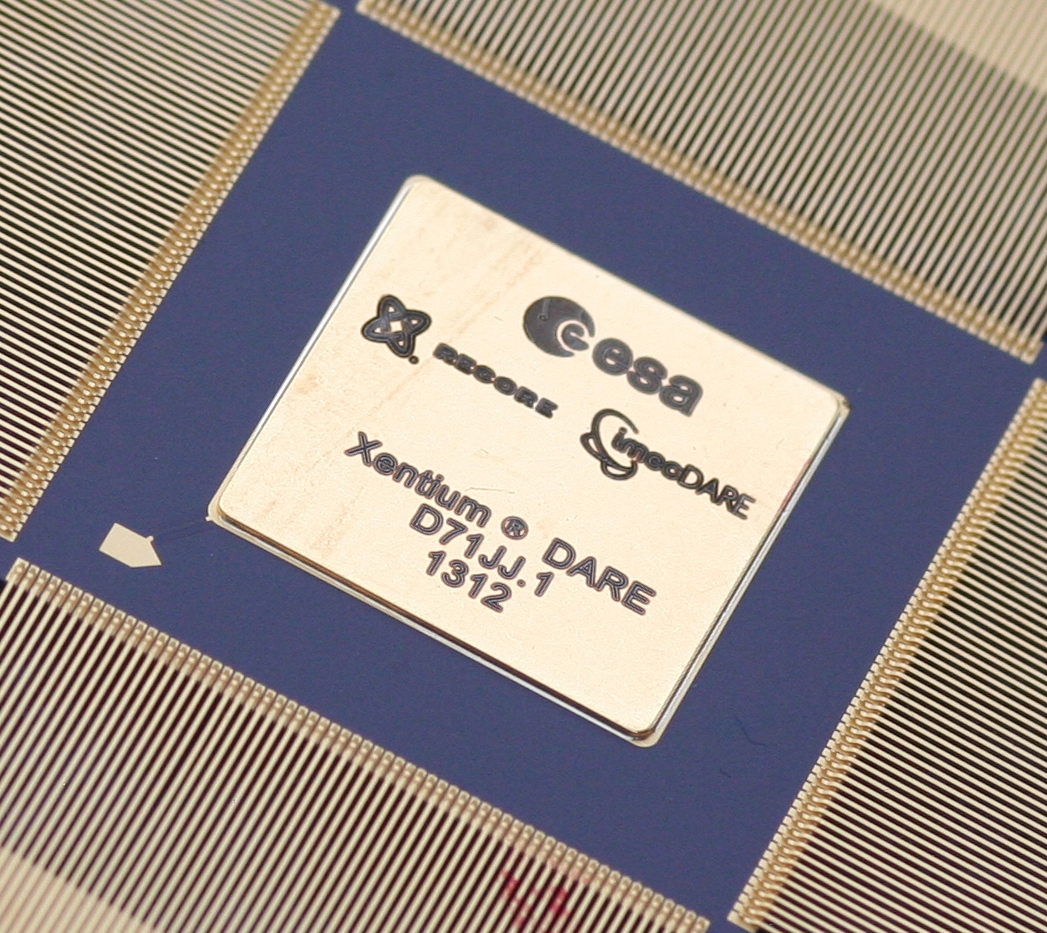

As we worked to produce a reliable data processor for space missions, we hardened key parts of the functional prototype design in 180nm CMOS technology, using the IMEC DARE libraries.

The ASIC prototype successfully passed functional testing under full radiation (SEL > 70 MeV/cm2/mg; SEE – SEU > 50 MeV/cm2/mg).

Scalable sensor data processor

The Xentium DSP cores have been licensed for, and integrated in the preliminary design of the Scalable Sensor Data Processor, which is a high-performance, scalable, rad-hard (~1 Mrad TID), highly-integrated mixed-signal data processor for sensors, instruments, and processing units for future science and exploration missions.

NASA/ESA-documents about SSDP:

Scalable sensor data processor: a multi-core payload data processor asic (pdf)

Scalable sensor data processor: development and validation (pdf)